Pengertian System Bus

Bus merupakan suatu alur lintasan yang digunakan oleh

komputer dalam berkomunikasi untuk menghubungkan dua atau lebih perangkat dalam

komputer (William, 2003). Bus memiliki karakteristik yaitu bus merupakan suatu

medium transmisi yang dipakai bersama. Apabila berbagai perangkat telah

terhubung ke bus maka jika perangkat-perangkat tersebut memancarkan sinyal,

maka sinyal tersebut dapat diterima oleh perangkat lain yang terhubung dalam

bus itu juga. Jika 2 perangkat melakukan transmisi dalam waktu yang bersamaan,

maka sinyal akan tumpang tindih . Oleh karena itu hanya ada satu perangkat saja

yang akan berhasil melakukan transmisi pada saat tertentu.

Pada umumnya suatu bus terdiri dari berbagai lintasan

komunikasi atau saluran. Masing-masing saluran pada bus tersebut mampu

mentransmisikan sinyal yang mewakili bilangan biner 1 dan bilangan biner 0.

Pada sistem komputer bisa saja berisi sejumlah bus berbeda yang menyediakan

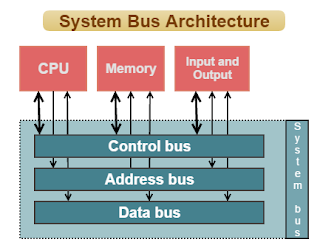

lintasan antara komponen-komponen dalam komputer. System bus adalah sebuah bus yang menghubungkan komponen-komponen

komputer utama yang terdiri dari prosesor, memori dan I/O (William, 2003).

2.2.

Struktur Bus

Didalam suatu sistem bus berisi sekitar 50 sampai

ratusan saluran terpisah. Masing-masing lintasan memiliki arti atau fungsi.

Saluran-saluran kontrol digunakan untuk mengontrol akses ke saluran alamat dan

saluran data. Karena data dan saluran alamat dipakai bersama oleh semua

komponen, jadi harus ada alat yang dapat mengendalikan penggunaannya. Saluran kontrol

umumnya meliputi (William, 2003):

- Memori tulis : data pada bus akan ditulis ke

dalam lokasi alamat.

- Memori baca : data dari lokasi alamat ditempatkan

pada bus.

- I/O tulis : data pada bus menjadi output ke

alamat port I/O.

- I/O baca : data dari port I/O yang beralamat

ditempatkan pada bus.

- Transfer ACK : menunjukkan bahwa data telah

diterima dari bus atau telah ditempatkan pada bus.

- Bus request:

menunjukkan suatu modul kontrol bus

- Bus grant

: menunjukkan bahwa modul yang melakukan permintaan telah diberi hak

kontrol bus.

- Interupsi request : menunjukkan bahwa suatu interupsi ditangguhkan.

- Interupsi ACK : bahwa interupsi yang

ditangguhkan telah diketahui.

- Clock

: yang digunakan untuk mensinkronkan operasi-operasi.

- Reset

: menginisialisasi semua modul.

2.3.

Teknik

Arbitrasi Bus

Arbitrasi bus adalah suatu proses

yang menentukan bus pengontrol (master) pada waktu yang diberikan ketika

terdapat permintaan satu pengontrol bus atau lebih (Syahrul,2010). Biasanya didalam komputer, processor

dan pengontrol DMA lah yang menjadi master bus, sedangkan memori dan I/O yang

menjadi slave nya. Sebuah slave ini tidak akan menjadi master bus

maka tidak dapat membuat penginilisasian terhadap siklus bus.

Bila terdapat lebih dari satu master

bus, maka yang dipakai hanya satu saja untuk mengontrol bus secara aktif. Tapi

yang lainnya hanya menunggu giliran pengontrolan bus. Dan disini yang

menentukan mana yang menjadi master bus ialah pengawas bus. Ada 2 macam

pengawas bus, yaitu (Syahrul,2010) :

a.

Arbitasi terpusat

Arbitrasi terpusat adalah

pengontrol bus atau arbiter tunggal, bertanggung jawab pada pengalokasian waktu

pada bus.

b.

Arbitrasi terdistribusi

Arbitrasi terdistribusi adalah

metode yang masing-masing mempunyai pengaksesan dalam logikanya, dan semuanya

saling bekerja sama, karena tidak adanya pengontrol bus.

2.4.

Jenis-jenis

Bus

Berdasarkan jenis-jenis bus pada komputer, bus dibedakan menjadi (William,2003) :

·

Dedicated Bus

Bus yang menyalurkan data

tertentu saja disebut dengan Dedicated Bus, seperti alamat saja atau data saja.

Kelebihan dedicated bus adalah through-put yang tinggi karna hanya ada sedikit

kemacetan yang terjadi pada sistem bus, sedangkan kekurangannya adalah ukuran dan biayanya meningkat pada sistem bus

komputer.

·

Multiplexed Bus

Multiplexed Bus adalah bus yang melalui informasi yang berbeda dalam

data, alamat dan sinyal kontrolnya dengan multipleks. kelebihan multiplexing

adalah penggunaan saluran-salurannya lebih sedikit, jadi dapat menghemat biaya

dan ruang dari sistem bus. Dan kekurangannyaa adalah rangkaian multiplexing

tersebut sangatlah rumit dan mengurangi potensi kerjanya karna pada saluran

yang sama tidak dapat berlangsung secara pararel.

2.5.

Siklus Bus

Karakteristik kunci dari suatu bus adalah penggunaan media transmisi

dengan secara bersamaan tetapi waktu nya yang tidak bersamaan. Jika ada dua

perangkat yang transmisi nya dalam waktu yang bersamaan, maka sinyal-sinyal

tersebut akan saling mengacaukan dan mengakibatkan kerusakan, jadi hanya ada

satu perangkat saja yang dapat ditransmisikan didalam suatu periode tertentu.

Siklus bus adalah urutan kejadian yang terjadi pada bus

dalam mentransfer satu kata informasi antara CPU (master) dan memori (Syahrul,2010). Untuk mengakses saluran data dan alamat digunakan bus kontrol.

Sinyal–sinyal yang ada pada bus kontrol akan mentransmisikan informasi dan

perintah pada sistem yang digunakan untuk mengindikasikan validitas data dan

alamat.

Berikut ini adalah beberapa siklus didalam bus pada saluran control (Syahrul,2010) :

a. Kontrol memori write

Kontrol

memori write digunakan agar data pada bus diberikan ke lokasi memori yang

teralamati

b. Kontrol memori read

memori

read digunakan agar data dari lokasi memori yang sudah teralamati ditempatkan

pad bus

c. Kontrol I/O write

I/O write digunakan agar data pada bus

diberikan ke I/O port yang teralamati

d. Kontrol I/O read

I/O read digunakan agar data dari I/O port

yang sudah teralamati ditempatkan pada bus

e. Kontrol transfer ACK

Transfer

ACK digunakan untuk mengindikasikan bahwa data telah diterima dari atau

ditempatkan disuatu bus

f.

Kontrol bus request

Bus

request digunakan untuk mengindikasikan bahwa suatu modul memerlukan perolehan

dari suatu kontrol bus

g. Kontrol bus grant

Bus

grant digunakan untuk mengindikasikan bahwa suatu permintaan modul telah

diberikan kontrol bus

h. Kontrol interrupt request

Interrupt

request digunakan untuk mengindikasikan bahwa suatu interupsi mengalami

penundaan

i.

Kontrol interrupt ACK

Interrupt

ACK digunakan untuk pengakuan bahwa interupsi yang tertunda telah dikenali oleh

sistem

j.

Kontrol clock

Clock

digunakan untuk pengoperasian sinkronisasi

k. Kontrol reset

Reset

digunakan untuk menginisialisasikan semua modul pada sistem bus

2.6.

Organisasi

Bus

Pengontrol I/O dapat dikoneksikan secara langsung ke bus-bus item dengan

cara menggunakan satu atau lebih bus ekspansi. Antarmuka bus ekspansi untuk

menyangga transfer data antara sistem bus dan pengontrol I/O.

Arsitektur bus tradisional dapat diterapkan karna efisiensi nya, tetapi

dalam kinerja yang lebih tinggi arstiektur ini tidak dapat mendukung perangkat

I/O. maka dalam hal ini diperlukan bus yang berkecepatan tinggi dimana hanya

memerlukan susunan suatu jembatan antara bus-bus. Susunan itulah yang dinamakan

dengan arsitektur loteng tengah. Konfigurasi arsitektur bus

tradisional

dapat dilihat pada gambar 2.1 berikut ini (Syahrul,2010) :

Gambar

2.1 Konfigurasi arsitektur bus

tradisional

Sedangkan dalam arsitektur bus dengan kecepatan tinggi, sistem bus lokal

itu mengkoneksikan processor ke

pengontrol cache lalu dikoneksikan

lagi ke sistem bus pendukung memori utama. Pengontrol cache tersebut

diintegrasikan ke perangkat penyangga untuk dikoneksikan lagi ke bus dengan

kecepatan tinggi. Keuntungan dari susunan arsitektur bus dengan kecepatan

tinggi ini ialah bus tersebut dapat membawa perangkat dengan tuntunan yang

tinggi lebih dekat dengan processor.

Agar processor dan bus dengan

kecepatan tinggi tetap dapat diterima dengan baik . Konfigurasi

arsitektur bus kecepatan tinggi dapat dilihat pada gambar 2.2 berikut ini (Syahrul,2010) :

No comments:

Post a Comment